### **REQUIREMENTS SPECIFICATION DOCUMENT**

#### SEPHY Grant No. 640243

#### **Deliverable Information**

| Work Package                       | 1 Dissemination Level of Deliverable <sup>1</sup> : |                 | of PU               |                 |

|------------------------------------|-----------------------------------------------------|-----------------|---------------------|-----------------|

| Deliverable Number                 |                                                     |                 | D2.1                |                 |

| Date of Issue                      |                                                     |                 | 21/07/2016          |                 |

| Document Reference                 | SEPHY                                               | ′-D2.1-Requir   | rements Specifi     | cation Document |

| Version Number                     |                                                     |                 | 2.0                 |                 |

| Nature of Deliverable <sup>2</sup> |                                                     | CD              | CO                  |                 |

| Keywords                           | Ne                                                  | etwork-level, A | oplication level, F | Requirements    |

<sup>&</sup>lt;sup>1</sup> Dissemination level: **PU** = Public; **PP** = Restricted to other programme participants (including the Commission Services); **RE** = Restricted to a group specified by the consortium (including the Commission Services); **CO** = Confidential, only for members of the consortium (including the Commission Services).

<sup>&</sup>lt;sup>2</sup> Nature of deliverable:  $\mathbf{\tilde{R}}$  = Report;  $\mathbf{P}$  = Prototype;  $\mathbf{\tilde{D}}$  = Demonstrator;  $\mathbf{O}$  = Other

#### Abstract

The requirements for integrated circuits that have to operate in space are very different from those that are used in terrestrial applications. In particular, the radiation is much more intense and causes several types of effects on the devices that compromise their reliability. Therefore, special "rad-hard" design and manufacturing techniques are needed for devices that will operate in space.

Therefore, in order to implement Ethernet in space systems, rad-hard Ethernet components have to be designed. This deliverable provides the guidelines to design and manufacture rad-hard Ethernet PHYs (Physical layer transceivers). In particular a 10/100Mbps PHY is targeted as the first short term objective. The SEPHY deliverable D2.1 specifies the requirements for the achievement of the project goals, i.e. the implementation of a rad-hard Ethernet transceiver component that can be used in space missions.

Requirements have been analyzed and consolidated in the following categories:

- Communication and standard compliance

- Interfaces

- Power and power consumption

- Clocks

- Environmental (radiation, temperature)

- Reliability and fault-tolerance

- Configuration

- Quality in Manufacturing

This gathered data will be used as basis for the elaboration of a feasibility and risk assessment document, the PHY architectural design as well as for the creation of validation and verification plans at block, transceiver and network level.

## **Document Authors**

| ENTITY                    | CONTRIBUTORS                                |

|---------------------------|---------------------------------------------|

| TTTech Computertechnik AG | Carolina Reyes, Arjan Geven, Christian Fidi |

# **Document Change Record**

| ISSUE   | DATE       | CHANGE<br>PROPOSAL № | AFFECTED PARAGRAPHS                                   | DESCRIBE CHANGE                                                                |

|---------|------------|----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|

| Draft 1 | 15.07.2015 |                      | All                                                   | Creation                                                                       |

| Draft 2 | 20.07.2015 |                      | Objectives, Use of D2.1 outcomes                      | Text added                                                                     |

| Draft 3 | 21.07.2015 |                      | Summary, Acronyms, Methodology                        | Text added                                                                     |

| Draft 4 | 23.07.2015 |                      | Appendix, Network and Application level requirements  | Text added                                                                     |

| Issue 1 | 31.07.2015 |                      | Deliverable D2.1 submitted                            | Closed deliverable                                                             |

| Draft 5 | 01.07.2016 |                      | Abstract                                              | Text added                                                                     |

| Draft 5 | 01.07.2016 |                      | Section 2. Network and application level requirements | Added text to clarify why functional and non-functional requirements encompass |

| Draft 5 | 01.07.2016 |                      | Section 2. Network and application level requirements | Added text to clarify which clauses of the 802.3 standard will be considered.  |

| Draft 6 | 15.07.2016 |                      | Subsection 2.1 Non-Functional requirements            | Edited requirements #5, #6, #15 and #16<br>to be more precise                  |

| Draft 6 | 16.07.2016 |                      | Subsection 2.1 Non-Functional requirements            | Added requirement #45, #46 and #47.                                            |

| Draft 6 | 16.07.2016 |                      | Subsection 2.2 Functional requirements                | Edited requirement #10 to be more<br>precise                                   |

| Draft 7 | 19.07.2016 |                      | Subsection 2.2 Functional requirements                | Added requirement #44                                                          |

| Issue 2 | 20.07.2016 |                      | D2.1 submitted                                        | Included feedback from review meeting                                          |

## **Disclosure Statement**

The information contained in this document is the property of S.A. ARQUIMEA Ingeniería S.L.U., and it shall not be reproduced, disclosed, modified or communicated to any third parties without the prior written consent of the abovementioned entities.

# **Table of Contents**

| Deliverable Information                                    |   |

|------------------------------------------------------------|---|

| Abstract                                                   | 2 |

| Document Authors                                           | 3 |

| Document Change Record                                     |   |

| 1 Introduction                                             | 6 |

| 1.1 Objectives                                             | 6 |

| 1.2 Use of the D2.1 outcomes                               | 6 |

| 1.3 Methodology used for the requirements definition phase | 7 |

| 2 Network and Application level requirements               | 8 |

| 2.1 Non-Functional Requirements1                           |   |

| 2.2 Functional Requirements1                               | 4 |

| 3 Summary1                                                 | 7 |

| 4 Acronyms1                                                | 8 |

| 5 Appendix1                                                | 9 |

## 1 Introduction

### 1.1 Objectives

The goal of this Network and Application level Requirements document is to provide detailed definitions of the set of requirements needed for the design and implementation of a 10/100 Ethernet physical layer transceiver.

## 1.2 Use of the D2.1 outcomes

The requirements are an important basis for other deliveries and work packages of the SEPHY project. They have been specified by the project partners based on their domain of expertise and on those activities to accomplish throughout the course of this project.

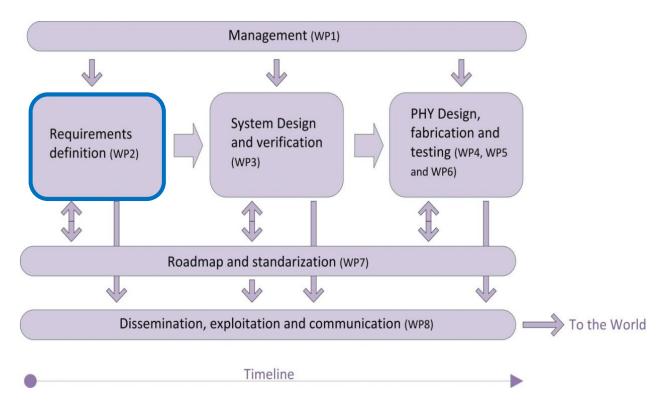

Work package WP2 will encompass the conditions to be satisfied for the development of the Ethernet PHY. These play an important role in WP3, for the system design and verification, as well as during the PHY design, fabrication and testing in WP4, WP5 and WP6.

The dependencies between the different work packages are illustrated Figure 1.

Figure 1. Interactions among all Work Packages

## 1.3 Methodology used for the requirements definition phase

The goal of this document is to provide a complete set of requirements for the development of the SEPHY transceiver. To this end, each partner has been requested to identify functional and non-functional requirements according to their area of expertise.

#### Phase 1: Bottom-up requirements collection

The requirements were collected in a bottom-up fashion based on the consortium expertise that covers:

- Analogue and digital design expertise

- Space system architecture expertise

- Manufacturing and process expertise

- Ethernet and standards expertise

- Space market expertise (launchers and satellites)

An input sheet has been provided to be filled with each partner's data as an initial input which was left free in order to come up with bottom-up requirements from each of the expertise areas.

#### Phase 2: Technical discussion and harmonization

Following the requirement collection phase the technical discussion phase started in order to iterate and align the requirements to each other and to discuss technical feasibility based on mutual understanding of capabilities and technical challenges and work out potential conflicting requirements. A single excel sheet collecting all requirements was created, distributed among the partners and used for discussion. This occurred in an iterative way in three iterations, where each partner had time to make changes to or comment on their own requirements and/or of those of the partners.

#### Phase 3: Consolidation phase

The consolidation phase aimed to eliminate repeated requirements, assure similar wording, set priorities. A compact version of the outcome of the consolidation phase listing the functional and non-functional requirements can be found in this document. An extended version is available in the Appendix section.

The link between the consolidated requirements and the initial requirements of the partners has been kept to enable backtracking in case of unclear issues.

## 2 Network and Application level requirements

The network level requirements encompass all functional and non-functional properties that shall be respected regarding the low level functionality of the physical layer. This reflects the requirements as posed by the IEEE 802.3 Ethernet specification, as well as various requirements with respect to operating environment, power consumption, management interface, packaging, and further specific requirements for space Ethernet.

The requirements at application level will provide an overview of those functionalities that the SEPHY chip needs to implement. TASE will, for instance, take the lead based on their experience at equipment, subsystem and system level. TTT will contribute to this task with the TTEthernet level perspective. ATMEL will participate in this task by sharing its extensive customer experience with all partners and will also be able to get specific information from key potential customers and end-users.

The requirements are split in two categories:

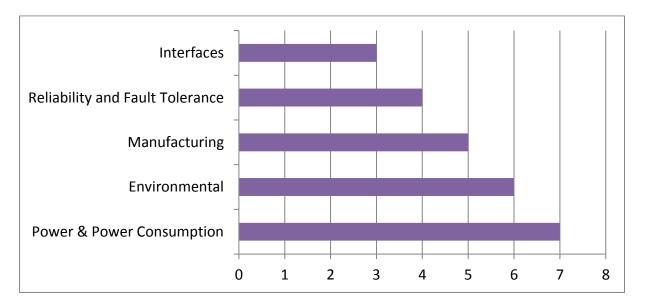

Non-functional: Composed of five subcategories – Power & Power Consumption, Environmental, Interfaces, Manufacturing, and Reliability and Fault-tolerance– with a total of twenty five requirements, from which twenty three were identified to have high priority and the rest low. Here, Power & Power Consumption as well as the Environmental subcategories turned out to collect most of the non-functional needs. See Figure 1 for a graphical representation.

Figure 2. Number of non-functional requirements sorted according to category

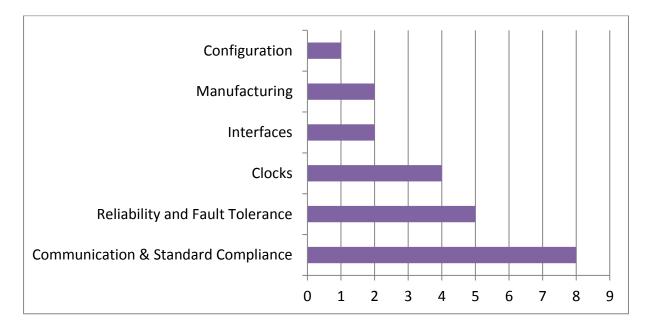

2. Functional: Composed of six subcategories – Communication and Standard Compliance, Reliability and Fault-tolerance, Clocks, Interfaces, Configuration, and Manufacturing – with a total of twenty two requirements, where sixteen were identified to be of high priority, one with medium and four with low priority. The subcategories Communication and Standard Compliance collected most of the functional needs together with Reliability and Fault-tolerance. See Figure 3 for a graphical representation.

Figure 3. Number of functional requirements sorted according to category

Note that both functional and non-functional requirements comprise manufacturing, reliability & fault tolerance and interfaces sub-categories. The difference here is that non-functional requirements relate to the specification of criteria that is used to judge the operation of the SEPHY PHY. On the other hand, those requirement categories defining specific behaviour or functions fall into the functional requirements category.

A key functional requirement is to be IEEE 802.3 (loose) standard-compliant. This means that basic requirements guaranteeing interoperability with other PHYs and with different MAC (for ground testing and potentially also in a space system) will be considered. This is captured in requirement 10, but deserves a more detailed explanation: the IEEE 802.3 standard is organized in clauses. Each clause covers an independent aspect of the standard, for example a PHY specification for a given speed and media type, a MAC interface or

specific features like auto-negotiation or energy efficient Ethernet. The clauses relevant to SEPHY are those related to 10/100 Mbps<sup>3</sup>, namely:

- Clause 14. Twisted-pair medium attachment unit (MAU) and baseband medium,

type 10BASE-T. This clause details the 10BASE-T PHY specifications.

- Clause 22. Reconciliation Sublayer (RS) and Media Independent Interface (MII). This clause details the 10/100 MAC interface specifications.

- Clause 24. Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) sublayer, type 100BASE-X. This clause details part of the 10BASE-TX PHY specifications.

- Clause 25. Physical Medium Dependent (PMD) sublayer and baseband medium, type 100BASE-TX. This clause details part of the 10BASE-TX PHY specifications.

There are a few requirements that are covered in other clauses of the standard. As those are however in most cases less critical, they have been marked as low priority requirements. These include for instance:

- Parallel Detection: Clause 28. Physical Layer link signalling for Auto-Negotiation on twisted pair Parallel detection function section "28.2.3.1 Parallel Detection".

- Energy Efficient Ethernet: Clause 78. Energy Efficient Ethernet (EEE).

The certification of SEPHY by an independent certification laboratory such as the Interoperability Laboratory at the University of New Hampshire is outside of the scope of the project. However, the verification process has been designed in a way that their test guidelines are followed so that in the future SEPHY could be certified if needed. The tests to be carried out for ensuring a basic level of compliance with the standard are described in detail in the deliverables D3.2 Verification Procedure at block level and D3.3 Verification Procedure at transceiver level.

In regard to those requirements addressing the total dose radiation tolerance (#1, #2, #3, #4 and #17), the following remark should be stated: the exact dose rates and the possible dose-rate effects that will be used for testing SEPHY (in the core MOS devices and/or in the bipolar devices used in the bandgap reference) will be specifically included in the test plan. These values will be described in detail in the D6.8 Radiation Plan and Report 1.

A compact version of the non-functional and functional requirements for both network and application level requirements is now introduced. Note the latter information before going through the tables:

• The word "Type" offers information regarding what type of requirement is evaluated.

<sup>&</sup>lt;sup>3</sup> For 100Mbps over twisted pair there are several PHY alternatives in the IEEE 802.3 standard like 100BASE-T4 or 100BASE-T1. For SEPHY only the 100BASE-TX option is relevant as it is the one implemented.

- "Requirements ID": each requirement is associated to a specific ID. This is helpful in case more specific information is searched in the extended excel sheet (see Appendix).

- "Description": provides an explanation of the requirement itself and what the devices or functions "shall" do.

The word "shall" identifies mandatory provisions of this document. It is reserved

exclusively for requirements and must not be used for any other meaning. A requirement must contain only one "shall".

• "Priority": This allows to identify the importance level of a requirement. "High" means that this is important to accomplish and "Low" is something that it is important to have, but it does not have major consequences if not achieved.

## 2.1 Non-Functional Requirements

| Туре          | Req.<br>ID | Description                                                                                                                                                                                                                                            | Priority |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Environmental | 1          | The Total Ionizing Dose (TID) shall be greater than<br>100krad. SEPHY regards this value, as it is used by<br>most of the space applications.                                                                                                          | High     |

|               | 3          | The SEU threshold LET shall be at least 30MeV/mg/cm <sup>2</sup> . It is important that the PHY supports operation under radiation conditions in deep space environment.                                                                               | High     |

|               | 4          | The SEU Error Rate, considering GEO orbit, shall be<br>lower than 10 <sup>-10</sup> errors/bit-day (at <70 MeV/mg/cm <sup>2</sup> ).<br>It is important that the PHY supports operation under<br>radiation conditions in deep space environment.       | High     |

|               | 17         | The SEL Threshold LET shall be greater than 70 MeV/mg/cm <sup>2</sup> . This is the maximum value that can be measured in European accelerators. It is necessary that the PHY supports operation under radiation conditions in deep space environment. | High     |

|                                   | 2  | The Total Ionizing Dose (TID) shall be greater than 300krad. This is the maximum TID value tested so far, and has low priority as it cannot be ensured.                                                                                                        | Low  |

|-----------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                   | 5  | During the test sequence, the chip shall withstand temperatures in the range of -55°C to +125°C. The operating environment in spacecraft fluctuates greatly in temperature and the chip should thus be able to endure this.                                    | High |

|                                   | 6  | The PHY shall be designed to be manufactured for<br>space-grade ceramic (ESCC9000 or QML-V) and<br>plastic packaging. The flexibility of packaging will<br>support different customer requests: ceramic for<br>launchers and plastic for development purposes. | High |

| Manufacturing                     | 13 | The package shall be of Quad Flat type (QFP) and shall have a maximum of 64 pins. A standard space package will be considered for design purposes.                                                                                                             | High |

|                                   | 34 | There shall be no floating grounds.                                                                                                                                                                                                                            | High |

|                                   | 45 | The chip shall be at least MSL1, hermetic for ceramic package and MSL3, non-hermetic for plastic package.                                                                                                                                                      | High |

|                                   | 46 | A traceability of the chips in the supply chain shall be possible.                                                                                                                                                                                             | High |

|                                   | 12 | The analogue and digital power domains shall be separated.                                                                                                                                                                                                     | High |

| Power and<br>power<br>consumption | 14 | The digital domain shall have its own external 1.8V supply. Fast switching digital supply voltage should be provided externally, as some electronic components are difficult to integrate on-chip.                                                             | High |

|                                   | 11 | The analogue domain shall have its own external 3.3V supply.                                                                                                                                                                                                   | High |

|                                    | 15 | ESD tolerance shall be 2 kV HBM (Class 2 / MIL-STD-<br>883H), 250V in CDM and higher than 100V in MM.                                                                                                                                                                      | High |

|------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                    | 26 | Special care shall be put during power supplies sequencing during start-up, to avoid excessive inrush-current.                                                                                                                                                             | High |

|                                    | 29 | The power dissipation shall be lower than 0.5W.                                                                                                                                                                                                                            | High |

|                                    | 43 | The PHY shall meet a power consumption target of <0.5W. This should enable its use in a wide range of applications that are power limited.                                                                                                                                 | High |

| Reliability and<br>Fault-tolerance | 16 | Chip lifetime in space environment shall be 20 years in GEO for the ceramic version and 10 years for the plastic version. The expected lifetime of the device has a big impact on the implementation of the chip.                                                          | High |

|                                    | 23 | The design shall accommodate manufacturing testability. It is important to provide adequate test interfaces and/or specifications that allow for efficient and automatic testing.                                                                                          | High |

|                                    | 25 | Fault-tolerant techniques that are used during the VHDL development phase shall be defined. It is important to regard the possible fault effects on the higher level of the digital design hierarchy, such as in counters, registers, reset and clock generation circuits. | High |

|                                    | 47 | The reliability of the chip shall be 1000 FIT. This will<br>ensure that the number of failures is at most in the<br>order of 1000 devices for 1 million hours.                                                                                                             | High |

| Interfaces                         | 27 | Digital interfaces shall be implemented with LVCMOS/LVTTL compatibility.                                                                                                                                                                                                   | High |

|                                    | 31 | An Enable function shall be externally provided through a pin.                                                                                                                                                                                                             | High |

| 28 | The transmitter and receiver interface shall be<br>compatible with cold spare. It is meaningful to have<br>high-impedance output and input pins for redundancy<br>(when needed). | Low |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | (when needed).                                                                                                                                                                   |     |

## 2.2 Functional Requirements

| Туре       | Req.<br>ID | Description                                                                                                                                                                                                    | Priority |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Interfaces | 7          | Access to the PHY for data transfer shall be provided to<br>the MAC by means of an RMII and MII interface. A<br>standard interface for data communication to the MAC<br>layer should be guaranteed.            | High     |

|            | 8          | Access to the PHY for management and diagnostics<br>shall be provided to the MAC by means of an MDIO<br>interface. A standard interface for management and<br>diagnostics to the MAC layer should be provided. | High     |

|            | 9          | The minimum MDIO clock rate shall be at least 2.5MHz.<br>Again, for validation purposes, a standard interface for<br>management and diagnostics to the MAC layer should<br>be provided.                        | High     |

| Clocks     | 18         | A clock (CLKIN) shall be externally provided through a pin. A clean external clock is the best reference source for clocking the device.                                                                       | High     |

|            | 19         | CLKIN shall be 25MHz. It should be compatible with other devices.                                                                                                                                              | High     |

|            | 20         | CLKIN clock jitter shall be 250 ps. This is important for                                                                                                                                                      | Medium   |

|                                             |    | the PLL design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|---------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                             | 10 | The PHY shall be loose IEEE 802.3 standard-compliant<br>with the clauses that are relevant to 10/100 over twisted<br>pair. In more detail, the following clauses should be<br>implemented:<br>- Clause 14. Twisted-pair medium attachment unit<br>(MAU) and baseband medium,<br>type 10BASE-T<br>- Clause 22. Reconciliation Sublayer (RS) and Media<br>Independent Interface (MII)<br>- Clause 24. Physical Coding Sublayer (PCS) and<br>Physical Medium Attachment (PMA) sublayer, type<br>100BASE-X.<br>- Clause 25. Physical Medium Dependent (PMD)<br>sublayer and baseband medium, type 100BASE-TX. | High |

| Communication<br>and standard<br>compliance | 21 | The PHY shall operate always in full duplex mode.<br>There is no shared media allowed for UTP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | High |

|                                             | 35 | In terms of latency, the PHY shall support a TTL between 250 and 500ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | High |

|                                             | 42 | The PHY shall support a cable length of up to 100m.<br>Since the power consumption is nearly the same for<br>50m & 100m, the selected cable length is 100m.                                                                                                                                                                                                                                                                                                                                                                                                                                               | High |

|                                             | 37 | The PHY shall support Parallel Detection (not full Auto-<br>negotiation).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Low  |

|                                             | 38 | The PHY shall support frame lengths of up to 8000 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Low  |

|                                             | 40 | The PHY shall support Energy Efficiency Ethernet (802.3az) by manual configuration (no Auto-negotiation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Low  |

|                                             | 41 | The PHY shall also support 100-BASE-FX for optical media to cover a wider market.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Low  |

| Configuration                               | 22 | All configuration registers shall be refreshed by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High |

|                 |    | a multility of the second second to exact the second state of the second s |         |

|-----------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                 |    | scrubbing. It is necessary to avoid the accumulation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

|                 |    | errors in those configuration registers that are not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|                 |    | continuously updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

|                 |    | Respect the 150nm design manuals rules/guidelines. In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

|                 | 24 | this way it is possible to guarantee the product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High    |

|                 |    | manufacturing capabilities at space level quality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| Manufacturing   |    | The chip shall be RoHS compliance. Dangerous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

|                 | 44 | substances commonly used in electronic and electronic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | High    |

|                 |    | equipment should be avoided.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C C     |

|                 |    | The PHY shall support Local Loopback mode for self-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|                 | 30 | testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | High    |

|                 |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

|                 |    | The PHY shall provide status indicators during                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

|                 |    | operation: Transmission, receptions & link activity pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

|                 | 32 | This should facilitate the interpretation of any hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | High    |

|                 |    | test and diagnostic procedures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| Reliability and |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| Fault-tolerance |    | The PHY shall integrate internal registers to monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 Beele |

|                 | 33 | faults during radiation testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High    |

|                 |    | The PHY shall support link integrity checking for cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

|                 | 36 | diagnostics, as it is part of the standard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | High    |

|                 | 39 | The PHY shall support loopback modes for testing and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|                 |    | when debugging installed devices. This will allow to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | High    |

|                 |    | norform covered turned of diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U       |

|                 |    | perform several types of diagnostics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

## 3 Summary

This document provides a list of Network and Application level Requirements that will be used throughout the course of the SEPHY project for the design, implementation and validation of the 10/100 Ethernet physical layer transceiver.

All these requirements were carefully selected by the partners to ensure that they are fully in line with the trend towards Ethernet based technologies for space applications.

# 4 Acronyms

|         | -                                                              |

|---------|----------------------------------------------------------------|

| CSMA/CD | Carrier Sense Multiple Access with Collision Detection         |

| ESCC    | European Space Components Coordination – Generic Specification |

| 9000    | No. 9000                                                       |

| ESD     | Electro Static Discharge                                       |

| FIT     | Failures In Time                                               |

| IEEE    | Institute of Electrical and Electronics Engineers              |

| LET     | Linear Energy Transfer                                         |

| LVCMOS  | Low Voltage Complementary Metal Oxide Semiconductor            |

| LVTTL   | Low Voltage Transistor Transistor Logic                        |

| MAC     | Media Access Control                                           |

| MDIO    | Management Data Input/Output                                   |

| MII     | Media-Independent Interface                                    |

| MSL     | Moisture Sensitivity Level                                     |

| PDK     | Process Design Kit                                             |

| PHY     | PHYsical layer                                                 |

| PLL     | Phase Locked Loop                                              |

| QFP     | Quad Flat Package                                              |

| QML     | Qualified Manufacturers List                                   |

| RH      | Relative Humidity                                              |

| RMII    | Reduced Media-Independent Interface                            |

| SEL     | Single Event Latch-up                                          |

| SEPHY   | Space Ethernet PHYsical layer                                  |

| SEU     | Single Event Upsets                                            |

| TID     | Total Ionizing Dose                                            |

| TTL     | Time to leave                                                  |

| UTP     | Unshielded Twisted Pair                                        |

| VHDL    | Very High Speed Integrated Circuits                            |

| WP      | Work Package                                                   |

|         | -                                                              |

# 5 Appendix

| Requirement<br>ID:<br><req. id=""></req.> | Category<br><functional<br>/ non-<br/>Functional&gt;</functional<br> | Sub Category<br><radiation,<br>Temperature,<br/>Packaging,<br/>etc&gt;</radiation,<br> | Description:<br><req. description=""></req.>                                                        | Verification<br>Method<br><description<br>how to verify&gt;</description<br> | Rationale:<br><the behind="" rationale="" this<br="">req.&gt;</the>                            | Priority<br><high,<br>Medium,<br/>Low&gt;</high,<br> |

|-------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1                                         | Non-<br>Functional                                                   | Radiation                                                                              | Total Ionizing Doze (TID) shall be greater than 100krad.                                            | Radiation<br>testing (T6.3.2,<br>T6.3.4)                                     | The PHY shall support<br>operation under radiation<br>conditions in deep space<br>environment. | 1 - High                                             |

| 2                                         | Non-<br>Functional                                                   | Radiation                                                                              | Total Ionizing Doze (TID) shall be greater than 300krad.                                            | Radiation<br>testing (T6.3.2,<br>T6.3.4)                                     | The PHY shall support<br>operation under radiation<br>conditions in deep space<br>environment. | 3 - Low                                              |

| 3                                         | Non-<br>Functional                                                   | Radiation                                                                              | The SEU threshold LET shall be at least 30MeV/mg/cm <sup>2</sup>                                    | Radiation<br>testing (T6.3.3,<br>T6.3.5)                                     | The PHY shall support<br>operation under radiation<br>conditions in deep space<br>environment. | 1 - High                                             |

| 4                                         | Non-<br>Functional                                                   | Radiation                                                                              | The SEU Error Rate shall be lower<br>than 10^-10 errors/bit-day (at <70<br>MeV/mg/cm <sup>2</sup> ) | Radiation<br>testing (T6.3.3,<br>T6.3.5)                                     | The PHY shall support<br>operation under radiation<br>conditions in deep space<br>environment. | 1 - High                                             |

| 5 | Non-<br>Functional | Temperature | The chip shall withstand<br>temperatures in the range of -55°C<br>to +125°C.                                      | Temperature<br>testing                    | Operating environment in spacecraft fluctuates greatly in temperature.  | 1 - High |

|---|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------|----------|

| 6 | Non-<br>Functional | Packaging   | The PHY shall be available in space-grade ceramic and plastic packaging                                           | Inspection                                | Flexibility of packaging will support different customer requests.      | 1 - High |

| 7 | Functional         | Interfaces  | Access to the PHY for data transfer<br>shall be provided to the MAC by<br>means of an RMII and MII interface      | Functional<br>testing (T6.2.2,<br>T6.2.3) | Provide standard interface for data communication to the MAC layer.     | 1 - High |

| 8 | Functional         | Interfaces  | Access to the PHY for<br>management/diagnostics shall be<br>provided to the MAC by means of<br>an MDIO interface. | Functional<br>testing (T6.2.2,<br>T6.2.3) | Provide standard interface for management/diagnostics to the MAC layer. | 1 - High |

| 9 | Functional         | Speed       | The minimum MDIO clock rate shall be at least 2.5MHz.                                                             | Functional<br>testing (T6.2.2,<br>T6.2.3) | Provide standard interface for management/diagnostics to the MAC layer. | 1 - High |

|    | 1 1        |                       |                                                                                                       | 1 | 1      |

|----|------------|-----------------------|-------------------------------------------------------------------------------------------------------|---|--------|

|    |            |                       | The PHY shall be loose IEEE 802.3                                                                     |   |        |

|    |            |                       | standard-compliant with the clauses                                                                   |   |        |

|    |            |                       | that are relevant to 10/100 over                                                                      |   |        |

|    |            |                       | twisted pair. In more detail, the                                                                     |   |        |

|    |            |                       | following clauses should be                                                                           |   |        |

|    |            |                       | implemented:                                                                                          |   |        |

|    |            |                       | - Clause 14. Twisted-pair medium                                                                      |   |        |

|    |            |                       | attachment unit (MAU) and                                                                             |   |        |

|    |            | I Standard compliance | baseband medium,                                                                                      |   |        |

| 10 |            |                       | type 10BASE-T                                                                                         |   | 4      |

| 10 | Functional |                       | - Clause 22. Reconciliation                                                                           |   | 1 - Hi |

|    |            |                       | Sublayer (RS) and Media                                                                               |   |        |

|    |            |                       | Independent Interface (MII)                                                                           |   |        |

|    |            |                       | - Clause 24. Physical Coding                                                                          |   |        |

|    |            |                       | Sublayer (PCS) and Physical                                                                           |   |        |

|    |            |                       | Medium Attachment (PMA)                                                                               |   |        |

|    |            |                       | sublayer, type 100BASE-X.                                                                             |   |        |

|    |            |                       | - Clause 25. Physical Medium<br>Dependent (PMD) sublayer and<br>baseband medium, type 100BASE-<br>TX. |   |        |

| 11 | Non-<br>Functional | Power       | The analogue domain shall have its own external 3.3V supply                                                                                                                                                                         | Inspection | see ARQ-003                                                                                                                                      | 1 - High |

|----|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 12 | Non-<br>Functional | Power       | Separated analogue and digital power domains                                                                                                                                                                                        | Inspection | Avoid interferences between analogue and digital domains                                                                                         | 1 - High |

| 13 | Non-<br>Functional | Packaging   | The package shall be of QFP type<br>and shall have a maximum of 64<br>pins                                                                                                                                                          | Inspection | A standard space package is recommended                                                                                                          | 1 - High |

| 14 | Non-<br>Functional | Power       | The digital domain shall have its own external 1.8V supply                                                                                                                                                                          | Inspection | Fast switching digital supply<br>voltage it is better to be<br>externally provided since big<br>capacitors are difficult to<br>integrate on-chip | 1 - High |

| 15 | Non-<br>Functional | Power       | ESD tolerance shall be 2 kV HBM (Class 2 / MIL-STD-883H) and 250V in CDM.                                                                                                                                                           | Inspection |                                                                                                                                                  | 1 - High |

| 16 | Non-<br>Functional | Reliability | Chip lifetime in space environment<br>shall be 20 years in GEO for the<br>ceramic version and 10 years for<br>the plastic version. The expected<br>lifetime of the device has a big<br>impact on the implementation of the<br>chip. | Analysis   | The expected lifetime of the device has a big impact on chip implementation                                                                      | 1 - High |

| 17 | Non-<br>Functional | Radiation     | The SEL Threshold LET shall be greater than 70 MeV/mg/cm <sup>2</sup> | Radiation<br>testing (T6.3.3,<br>T6.3.5)  | The PHY shall support<br>operation under radiation<br>conditions in deep space<br>environment.         | 1 - High   |

|----|--------------------|---------------|-----------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------|------------|

| 18 | Functional         | Clocks        | A clock (CLKIN) shall be externally provided through a pin            | Inspection                                | A clean external clock is the best reference source for clocking the device.                           | 1 - High   |

| 19 | Functional         | Clocks        | CLKIN shall be 25MHz                                                  | Inspection                                | Compatibility with other devices                                                                       | 1 - High   |

| 20 | Functional         | Clocks        | CLKIN clock jitter shall be 250 ps                                    | Inspection                                | Required for PLL design                                                                                | 2 - Medium |

| 21 | Functional         | Communication | The PHY shall operate always in full duplex mode                      | Verification and<br>Functional<br>testing | No shared media is allowed for UTP.                                                                    | 1 - High   |

| 22 | Functional         | Configuration | All configuration registers shall be refreshed by scrubbing.          | Verification and<br>Functional<br>testing | Avoid the accumulation of<br>errros in configuration<br>registers that are not<br>continuously updated | 1 - High   |

| 23 | Non-<br>Functional | Quality         | The design shall accommodate manufacturing testability                                                                  | Manufacturing<br>testability<br>review                                   | Provide adequate test<br>interface/specification to<br>allow efficient automatic test<br>(probe/test)                                                                                                                                                                           | 1 - High |

|----|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 24 | Functional         | Quality         | Respect 150nm Design Manuals<br>rules/guidelines                                                                        | Run geometric<br>checker,<br>connectivity<br>checker and<br>DRV checker. | Guarantee the product<br>manufacturing capability at<br>space level quality                                                                                                                                                                                                     | 1 - High |

| 25 | Non-<br>Functional | Fault-tolerance | Fault-tolerant techniques that are<br>used during the VHDL development<br>phase shall be defined                        | Basic functional<br>testing with<br>fault-injection                      | As the flip-flop cells, from<br>Atmel RH standard cell<br>library are already TMR<br>based it is important to take<br>care about fault effects on<br>the higher level of the digital<br>design hierarchy - counters,<br>registers, reset and clock<br>generation circuits, etc. |          |

| 26 | Non-<br>Functional | Power supply    | Special care shall be put during<br>power suplies secuencing durning<br>start-up, to avoid excesive inrush-<br>current. | Design                                                                   |                                                                                                                                                                                                                                                                                 | 1 - High |

| 27 | Non-<br>Functional | Interfaces        | Digital interfaces shall be<br>implemented with LVCMOS/LVTTL<br>compatibility. | Functional<br>testing (T6.1) |                                                                      | 1 - High |

|----|--------------------|-------------------|--------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------|----------|

| 28 | Non-<br>Functional | Interfaces        | The TX/RX interface shall be<br>compatible with cold spare                     | Functional<br>testing (T6.1) | High-impedance output/input<br>pins for redundancy in case<br>needed | 3 - Low  |

| 29 | Non-<br>Functional | Power dissipation | The power dissipation shall be lower than 0.5W                                 | Functional testing (T6.1)    |                                                                      | 1 - High |

| 30 | Functional         | Self-test         | The PHY shall support Local Loopback mode.                                     | Functional<br>testing (T6.1) | PHY testing (T6.1 & T6.3) & BIST                                     | 1 - High |

| 31 | Non-<br>Functional | Interfaces        | An Enable function shall be externally provided through a pin                  | Functional<br>testing (T6.1) | Power control                                                        | 1 - High |

| 32 | Functional         | Operation         | The PHY shall provide status<br>indicators: TX, RX & Link activity<br>pins     | Functional<br>testing (T6.1) | Hardware diagnostic & test                                           | 1 - High |

| 33 | Functional         | Fault-tolerance<br>monitoring | The PHY shall integrate internal registers to monitor faults during radiation testing | Radiation<br>testing (T6.3)               | A method to monitor<br>detection and correction<br>errors will be required to<br>validate fault-tolerance<br>techniques. | 1 - High |

|----|--------------------|-------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------|

| 34 | Non-<br>Functional | Packaging                     | No floating grounds                                                                   | Design                                    | Package groung plane.                                                                                                    | 1 - High |

| 35 | Functional         | Latency                       | Time to link (delay from power up to packet transmission)                             | Verification and<br>Functional<br>testing | The PHY shall support a TTL between 250 and 500ms.                                                                       | 1 - High |

| 36 | Functional         | Cable<br>Diagnostics          | Support Cable diagnostics                                                             | Verification and<br>Functional<br>testing | The PHY shall support link<br>integrity checking, as it is part<br>of the standard.                                      | 1 - High |

| 37 | Functional         | Auto-Neg                      | Parallel Detection                                                                    | Verification and<br>Functional<br>testing | The PHY shall support<br>Parallel Detection (not full<br>autoneg).                                                       | 3 - Low  |

| 38 | Functional         | Packet length                 | Jumbo frames                                                                          | Verification and<br>Functional<br>testing | The PHY shall support frame lenghts of up to 8000 bits.                                                                  | 3 - Low  |

| 39 | Functional         | Diagnostics                   | Loopback modes:<br>RMII,PCS,PMD,AFE                                                   | Verification and<br>Functional<br>testing | They PHY shall support<br>loopback modes for testing<br>and debugging installed<br>devices.                              | 1 - High |

| 40 | Functional         | Energy<br>Efficiency | Energy Efficiency Ethernet<br>(802.3az)      | Verification and<br>Functional<br>testing | The PHY shall support<br>Energy Efficiency Ethernet by<br>manual configuration (no<br>Autoneg).                                                                                                                                             | 3 - Low  |

|----|--------------------|----------------------|----------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|