# SEPHY DATASHEET

SEPHY Grant No. 640243

### **Deliverable Information**

| Work Package                       | 6                                  | 6 Dissemination Level of Deliverable <sup>1</sup> : |     | of PU |

|------------------------------------|------------------------------------|-----------------------------------------------------|-----|-------|

| Deliverable Number                 | D6.13                              |                                                     |     |       |

| Date of Issue                      | 14/12/2018                         |                                                     |     |       |

| Document Reference                 | D6.13 SEPHY DATASHEET              |                                                     |     |       |

| Version Number                     |                                    |                                                     | 1.1 |       |

| Nature of Deliverable <sup>2</sup> | R⊠                                 | P□                                                  | D   | O□    |

| Keywords                           | Guidelines, Rules, Recommendations |                                                     |     |       |

### Abstract

This document contains a description of the SEPHY chip, its basic functionality, pinout and modes.

<sup>&</sup>lt;sup>1</sup> Dissemination level: **PU** = Public; **PP** = Restricted to other programme participants (including the Commission Services); **RE** = Restricted to a group specified by the consortium (including the Commission Services); **CO** = Confidential, only for members of the consortium (including the Commission Services).

<sup>&</sup>lt;sup>2</sup> Nature of deliverable:  $\mathbf{R}$  = Report;  $\mathbf{P}$  = Prototype;  $\mathbf{D}$  = Demonstrator;  $\mathbf{O}$  = Other

# **Document Authors**

| ENTITY | CONTRIBUTORS     |  |

|--------|------------------|--|

| ARQ    | López, Jesús     |  |

|        | Gutierro, Úrsula |  |

| IHP    | Krstic, Milos    |  |

# Document Change Record

| ISSUE   | DATE       | CHANGE PROPOSAL № | AFFECTED<br>PARAGRAPHS | DESCRIPCIÓN DEL CAMBIO<br>CHANGE DESCRIPTION |

|---------|------------|-------------------|------------------------|----------------------------------------------|

| Issue 1 | 27/04/2017 | 1                 | All                    | Creation                                     |

### **Disclosure Statement**

The information contained in this document is the property of S.A. ARQUIMEA Ingenieria S.L (ARQ), THALES ALENIA SPACE ESPANA, SA (TASE), UNIVERSITAS NEBRISSENSIS, SA (UAN), IHP GMBH – INNOVATIONS FOR HIGH PERFORMANCE MICROELECTRONICS/LEIBNIZ-INSTITUT FUER INNOVATIVE MIKROELEKTRONIK (IHP), ATMEL NANTES SAS (ATM), TTTECH COMPUTERTECHNIK (TTT) and it shall not be reproduced, disclosed, modified or communicated to any third parties without the prior written consent of the abovementioned entities.

# **Table of Contents**

|        | le Information                                 |    |

|--------|------------------------------------------------|----|

|        |                                                |    |

|        | t Authors                                      |    |

|        | t Change Record                                |    |

|        | Contents                                       |    |

|        | oles                                           |    |

|        | ures<br>onyms                                  |    |

|        | Summary                                        |    |

|        | EIVER                                          |    |

|        |                                                |    |

|        | Ξδ                                             |    |

| 1 SYST | FEM DIAGRAM                                    | 11 |

| 2 RADI | ATION HARDENING                                | 12 |

|        | LABLE OPTIONS                                  |    |

|        | DIAGRAM                                        |    |

|        | CAL APPLICATION                                |    |

|        |                                                |    |

|        | ABSOLUTE MAXIMUM RATINGS                       |    |

|        | RECOMMENDED OPERATING CONDITIONS               |    |

| 6.3 E  | DC SPECIFICATIONS                              | 17 |

| 6.3.1  | TTL Input/Output Electrical Characteristics    | 17 |

| 6.3.2  | Power Consumption                              | 17 |

| 6.3.1  | Timing Characteristics                         | 18 |

| 7 FUNC | CTIONAL DESCRIPTION                            | 19 |

| 7.1 1  | 0BASE-T/100BASE-TX Driver                      | 19 |

| 7.2 N  | All Interface                                  | 20 |

| 7.3 F  | RMII Interface                                 | 20 |

| 7.4 N  | /II Interface                                  | 20 |

| 7.4.1  | MI Access Protocol                             | 20 |

| 8 ARCH | HITECTURE                                      | 23 |

|        | 00BASE-TX Transmitter                          |    |

| 8.2 1  | 00BASE-TX Receiver                             | 24 |

| 8.2.1  | Analog Front End                               | 24 |

| 8.2.2  | Digital Signal Processor                       | 24 |

| 8.2.3  | Digital Adaptive Equalization and Gain Control | 25 |

| 8.3 1  | I0BASE-T Transceiver                           | 26 |

| 8.3.1  | Normal Link Pulse Detection/Generation         | 26 |

| 8.3.2  | Transmit and Receive Filtering                 | 27 |

| 8.3.3  |                                                |    |

| 8.3.4  | Receiver                                       | 27 |

| 9<br>9   | CON<br>.1  | NFIGURATION<br>SPEED Pin Control                   |    |

|----------|------------|----------------------------------------------------|----|

| 9        | .2         | PHY Address                                        |    |

| 9        | .3         | LED Interface                                      |    |

| 9        | .4         | Internal Loopback                                  |    |

| 9        | .5         | Power Down                                         |    |

| 9        | .6         | Clock Input                                        | 28 |

| 9        | .7         | MII/RMII interface                                 |    |

| 9        | .8         | Power Up Sequence                                  |    |

| 9        | .9         | PLL power supply decoupling                        | 29 |

| 9        | .10        | PCB design recommendations                         | 29 |

| 9        | .11        | RESET OPERATION                                    | 29 |

|          | 9.11       | .1 Hardware Reset                                  | 29 |

|          | 9.11       | .2 Software Reset                                  | 29 |

| 10       |            | Il management Registers                            |    |

| N        |            | gisters definition                                 |    |

|          | 0          | ister Bit Acronyms                                 |    |

| N        |            | egisters Definition                                |    |

|          |            | trol Register (0x00)                               |    |

|          |            | us Register (0x01)                                 |    |

|          |            | (Identifier Register 1 (0x02)                      |    |

|          |            | (Identifier Register 1 (0x03)                      |    |

|          |            | config (0x10)                                      |    |

|          |            | config (0x11)                                      |    |

|          |            | t config (0x12)                                    |    |

|          |            | = Read only, LL = Latching low, LH = Latching high |    |

|          |            | trol 1 config (0x13)                               |    |

|          |            | TUS 1 (0x14)                                       |    |

|          |            | t MI register (0x1F)                               |    |

| 11<br>12 |            | INOUT DESCRIPTION                                  |    |

| 13       | SI<br>13.1 | UPPLY/GROUNDING LAYOUT, THERMAL RECOMMENDATIONS    | 50 |

|          | 13.1       | .2 Routing                                         | 50 |

|          | 13.1       | .3 Power decoupling                                | 50 |

|          | 13.1       | .4 Clock jitter                                    | 50 |

|          | 13.1       | .5 Thermal dissipation                             | 50 |

|          | 13.1       | .6 ESD caution                                     | 50 |

# List of Tables

| Table 0-1 – List of acronyms                 | 8 |

|----------------------------------------------|---|

| Table 6-1 - Recommended Operating Conditions |   |

| Table 7-1 - MI Interface Protocol            |   |

| Table 11-1 - SEPHY pin list                  |   |

# **List of Figures**

| Figure 1-1: SEPHY system diagram                                     |               |

|----------------------------------------------------------------------|---------------|

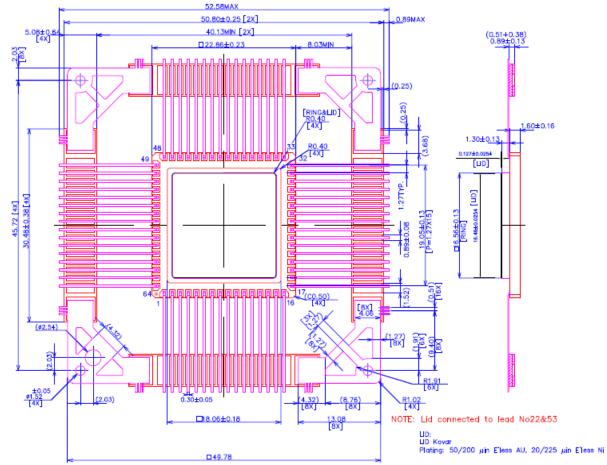

| Figure 4-1: SEPHY pinout                                             |               |

| Figure 5-1 Typical Application Circuit                               |               |

| Figure 7-1 MI Interface Write/Read Operations                        |               |

| Figure 8-1 100BASE-TX Block Diagram                                  | 23            |

| Figure 8-2 100BASE-TX Receive Block Diagram                          |               |

| Figure 8-3 EIA/TIA Attenuation vs. Frequency for 0, 50, 100, 130 and | 150 meters of |

| CAT 5 cable                                                          |               |

| Figure 12-1: SEPHY CQF64 package                                     |               |

# List of Acronyms

| ACRONYM | MEANING                                 |

|---------|-----------------------------------------|

| AAF     | Anti Aliasing Filter                    |

| ADC     | Analog to Digital Converter             |

| ASIC    | Application-Specific Integrated Circuit |

| CDM     | Charged Device Model                    |

| DAC     | Digital to Analog Converter             |

| DRV     | Driver                                  |

| ENOB    | Effective Number Of Bits                |

| ESD     | Electro Static Discharge                |

| GMII    | Gigabit Media Independent Interface     |

| НВМ     | Human Body Model                        |

| LET     | Liner Energy Transfer                   |

| MDC     | Management Data Clock                   |

| MDIO    | Management Data I/O                     |

| MII     | Media Independent Interface             |

| ММ      | Machine Model                           |

| PD      | Phase Detector                          |

| PGA     | Programmable Gain Amplifier             |

| PLL     | Phase Lock Loop                         |

| ΡΤΑΤ    | Proportional To Absolute Temperature    |

| RHA     | Radhard                                 |

| RMII    | Reduced Media Independent Interface     |

| RH      | Radiation Hardened                      |

| SEPHY   | Space Ethernet PHY                      |

| SEL     | Single Event Latch-up                   |

| SEU | Single Event Upset            |

|-----|-------------------------------|

| тс  | Test Chip                     |

| TID | Total Ionizing Dose           |

| ТМІ | Test Management Interface     |

| VCO | Voltage Controlled Oscillator |

Table 0-1 – List of acronyms.

# **Executive Summary**

This document contains a description of the SEPHY chip, its basic functionality, pinout and modes for the final user.

# **SEPHY** RADIATION HARDENED SINGLE PORT 10/100 MB/S ETHERNET PHYSICAL LAYER TRANSCEIVER

# **OVERVIEW**

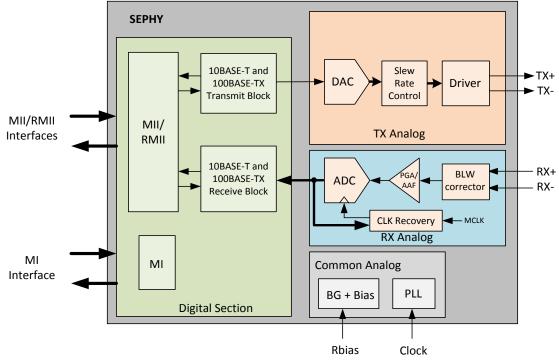

SEPHY is a Physical Layer device for Ethernet 10BASE-T and 100BASE-TX using category 5 Unshielded, Type 1 Shielded cables suitable for use in harsh and radiation environments. It integrates all the physical-layer functions needed to transmit and receive data. This device supports the standard and reduced Media Independent Interface (MII/RMII) for direct connection to a Media Access Controller (MAC)

SEPHY uses mixed-signal processing to perform equalization, data recovery, and error correction to achieve robust operation over CAT 5 twisted-pair wiring.

# **FEATURES**

- IEEE 802.3 10BASE-T compatible.

- IEEE 802.3 100BASE-TX compatible.

- ANSI X3.263-1995 compatible.

- Integrated high performance 100 Mb/s clock recovery circuitry requiring no external filters.

- Full Duplex support for 10 and 100 Mb/s.

- Programmable loopback modes for easy system diagnostics.

- 3.3V/1.8V power supply.

- Extended temperature range from -55°C to 125°C.

- Cold spare functionality.

- MII/RMII MAC communication interface.

- MI interface for MAC management and diagnostics.

- 15 years lifetime at maximum operating conditions.

- TID hardness greater than 100krad.

- SEU threshold LET>30MeV· cm<sup>2</sup>/mg.

- SEU Error Rate lower than 10<sup>-10</sup> errors/bit-day (@ <62 MeV⋅ cm²/mg).</li>

- SEL Threshold LET greater than 62 MeV· cm<sup>2</sup>/mg.

- QFP64 package

# 1 SYSTEM DIAGRAM

Figure 1-1: SEPHY system diagram

# **2** RADIATION HARDENING

| PARAMETER | MIN | ТҮР | МАХ | UNIT                   | COMMENTS              |

|-----------|-----|-----|-----|------------------------|-----------------------|

| TID       | -   | 100 | 300 | Krad                   |                       |

| SEL       | 62  | -   | -   | MeVcm <sup>2</sup> /mg |                       |

| SEU/SET   | 30  | -   | -   | MeVcm²/mg              |                       |

| SEU/SET   | -   | 62  | -   | MeVcm²/mg              | BER=10 <sup>-10</sup> |

# **3 AVAILABLE OPTIONS**

| PRODUCT | Quality<br>Level | PACKAGE | OPERATING<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA      |

|---------|------------------|---------|-----------------------------------|--------------------|-------------------------|

| SEPHY-S | S - Space        | TBD     | D -55°C to 125°C TBD              |                    | 250-piece tray<br>(TBC) |

| SEPHY-I | I - Industrial   | TBD     | TBD                               | TBD                | 250-piece tray<br>(TBC) |

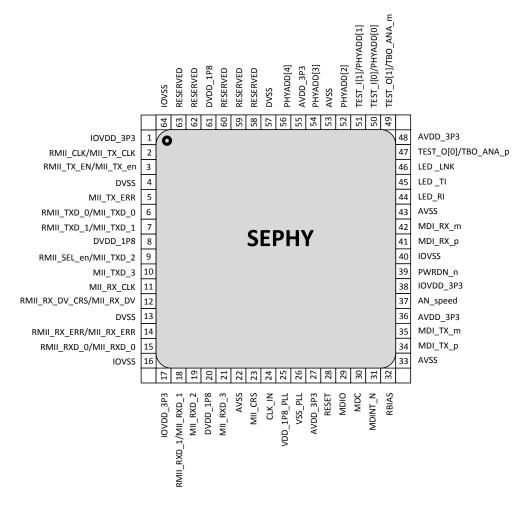

## 4 PIN DIAGRAM

Sephy

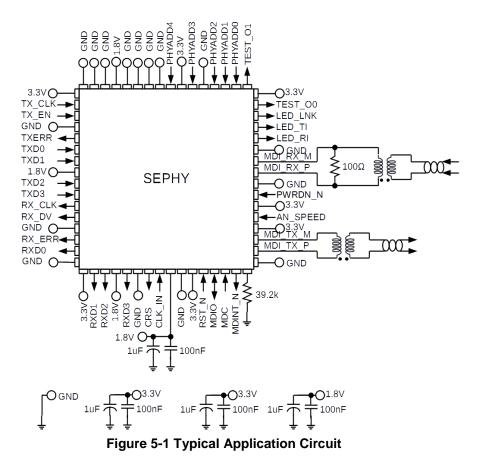

# **5 TYPICAL APPLICATION**

# **6 ELECTRICAL SPECIFICATIONS**

### 6.1 ABSOLUTE MAXIMUM RATINGS

| Description                       | Symbol              | Maximum rating      | Units |

|-----------------------------------|---------------------|---------------------|-------|

| I/O Supply Voltage                | AVDD_3P3            | -0.5 to 3.6         | V     |

| Core Supply Voltage               | DVDD_1P8            | -0.5 to 2           | V     |

| PLL Supply Voltage                | VDD_PLL_1P8         | -0.5 to 2           | V     |

| I/O pins                          | N/A                 | -0.5 to 3.6         | V     |

| Storage Temperature               | Тѕтс                | -65 to 150          | °C    |

| Operating Junction Temperature    | TJ                  | -55 to 150          | °C    |

| Soldering lead temperature (10 s) | T <sub>SOL</sub>    | 300                 | °C    |

| ESD                               | Vнвм<br>Vcdm<br>Vмм | 2000<br>250<br>>100 | v     |

**Note**: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 6.2 RECOMMENDED OPERATING CONDITIONS

| Description                          | Symbol          | Min  | Nom | Max  | Units |

|--------------------------------------|-----------------|------|-----|------|-------|

| I/O Supply Voltage                   | AVDD_3P3        | 3    | 3.3 | 3.6  | V     |

| Core Supply Voltage                  | DVDD_1P8        | 1.62 | 1.8 | 1.98 | V     |

| PLL Supply Voltage                   | VDD_PLL_1P8     | 1.62 | 1.8 | 1.98 | V     |

| Input High Voltage<br>(LVTTL&LVCMOS) | Vін             | 2    |     | 3.6  | V     |

| Input Low Voltage<br>(LVTTL&LVCMOS)  | VIL             | 0    |     | 0.8  | V     |

| Output High Voltage<br>(LVTTL)       | V <sub>OH</sub> | 2.4  |     |      | V     |

| Output Low Voltage<br>(LVTTL)        | Vol             | 0    |     | 0.4  | V     |

Table 6-1 - Recommended Operating Conditions

Sephy

# 6.3 DC SPECIFICATIONS

### 6.3.1 TTL Input/Output Electrical Characteristics

|                 | Parameter          | Min | Nom | Мах | Units |

|-----------------|--------------------|-----|-----|-----|-------|

| Vін             | Input High Voltage | 2   |     |     | V     |

| VIL             | Input Low Voltage  |     |     | 0.8 | V     |

| Ін              | Input High Current |     |     |     | μΑ    |

| Ι <sub>ΙL</sub> | Input Low Current  |     |     |     | μΑ    |

| Vон             | Output Low Voltage | 2.4 |     |     | V     |

| Vol             | Output Low Voltage |     |     | 0.4 | V     |

| loz             | Tri-State Leakage  |     |     | 10  | μΑ    |

| lcs             | Cold Spare Leakage |     |     | 10  | μΑ    |

### 6.3.2 Power Consumption

|                    | Parameter       | Min | Nom | Max                     | Units |

|--------------------|-----------------|-----|-----|-------------------------|-------|

| I <sub>dd100</sub> | 100BASE-TX      |     |     | 250 (1.8V)<br>60 (3.3V) | mA    |

| I <sub>dd10</sub>  | 10BASE-T        |     |     | 33 (1.8V)<br>64 (3.3V)  | mA    |

| I <sub>PD</sub>    | Power Down Mode |     |     | TBD                     | mA    |

# 6.3.1 Timing Characteristics

|                     | Parameter               | Min | Nom  | Мах | Units |

|---------------------|-------------------------|-----|------|-----|-------|

| t <sub>LAT100</sub> | Latency Time 100BASE-TX |     | 420  |     | ns    |

| tlat10              | Latency Time 10BASE-T   |     | 2100 |     | ns    |

# 7 FUNCTIONAL DESCRIPTION

SEPHY 10/100 Mb/s Ethernet Physical Layer integrates a 100BASE-TX Physical Coding Sub-layer (PCS) and a complete 10BASE-T module in a single chip. It provides a standard Media Independent Interface (MII) and reduced Independent Interface (RMII) to communicate between the Physical Signalling and the Medium Access Control (MAC) layers for both 100BASE-TX and 10BASE-T operations. It has a Management interface (MI) in order to access the configuration registers.

The 10BASE-T section of the device consists of the transmitter and receiver blocks.

- Transmitter

- MAU transmit functions

- Manchester encoder

- Wave-shaping FIR

- o 10BASE-T Driver

- Receiver

- MAU receive functions

- Manchester decoder

- 10BASE-T clock recovery

- Reception FSM

The 100BASE-TX section of the device consists of the following functional blocks:

- Transmitter

- o 4B/5B Encoder

- o NRZ Encoder

- Scrambler

- MLT3 encoder

- 100BASE-TX Driver

- Receiver

- o 4B/5B Decoder

- NRZ Decoder

- o Scrambler

- MLT3 Decoder

- Baseline Wander Correction

- Clock recovery module

- Programmable Gain Amplifier

The 100BASE-TX and 10BASE-T sections share the following functional blocks:

- TX DAC

- RX ADC

- MII status/control registers

- MI interface

#### 7.1 10BASE-T/100BASE-TX Driver

The output driver is a dual current-mode driver which can be switched to different current/speed depending on the transmission mode. The driver output is self-biased with no need for external biasing. A 100 $\Omega$  resistor should be placed in the receiver side between positive and negative terminals (MDI\_RX\_p, MDI\_RX\_m) in order to achieve the proper current/voltage conversion.

### 7.2 MII Interface

SEPHY incorporates the media independent interface (MII) as specified in Clause 22 of the IEEE802.3u standard. This interface may be used to connect PHY devices to a MAC in 10/100 Mb/s systems. The MII data interface consists of a receive bus and a transmit bus each with control signals to facilitate data transfer between the PHY and the upper layer (MAC). TX and RX clocks should run at 25MHz.

### 7.3 RMII Interface

SEPHY incorporates the reduced media independent interface (RMII) to reduce the number of pins in relation to MII, as specified in the RMII specification (rev1.2) from the RMII Consortium. This interface may be used to connect PHY devices to a MAC in 10/100 Mb/s systems. The RMII data interface consists of a receive bus and a transmit bus each with control signals to facilitate data transfer between the PHY and the upper layer (MAC). RMII clock should run at 50MHz.

### 7.4 MI Interface

The MI specification defines a set of thirty-two 16-bit status and control registers that are accessible through the management interface pins MDC and MDIO. SEPHY implements all the required MI registers as well as several optional registers. A description of the serial management access protocol follows.

#### 7.4.1 MI Access Protocol

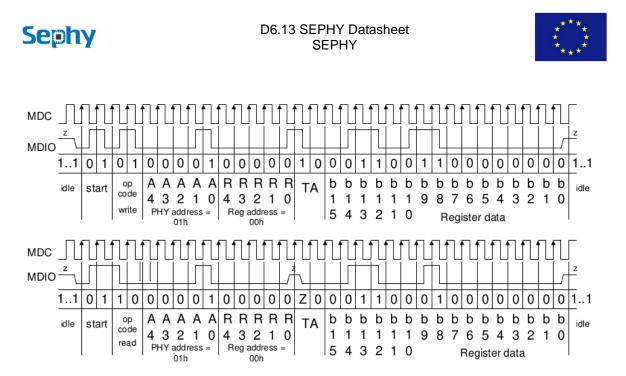

The MI interface consists of two pins, management data clock (MDC) and management data input/output (MDIO). MDC has a maximum clock rate of 25 MHz and no minimum rate. The MDIO line is bi-directional and may be shared by up to 32 devices with unique PHYADD. The MDIO frame format is shown below in Table 7-1.

The MDIO pin requires a pull-up resistor  $(1.5 \text{ k}\Omega)$  which, during IDLE and turnaround, will pull MDIO high. To initialize the MDIO interface, the station management entity sends a sequence of 32 contiguous logic ones on MDIO to provide SEPHY with a sequence that can be used to establish synchronization. This preamble may be generated either by driving MDIO high for 32 consecutive MDC clock cycles. In addition 32 MDC clock cycles should be used to re-sync the device if an invalid start, opcode, or turnaround bit is detected.

SEPHY waits until it has received this preamble sequence before responding to any other transaction. Once SEPHY MI port has been initialized no further preamble sequencing is required until after a power-on/reset, invalid start, invalid opcode, or invalid turnaround bit has occurred.

The start code (ST) is indicated by a <01> pattern. This assures the MDIO line transitions from the default idle line state. The operation code (OP) for a read transaction is <10>, while the operation code for a write transaction is <01>. Turnaround (TA) is defined as an idle bit time inserted between the register address field and the data field. To avoid contention during a read transaction, no device shall actively drive the MDIO signal during the first bit of turnaround. The addressed SEPHY drives the MDIO with a zero for the second bit of

turnaround and follows this with the required data. Figure 7-1 MI Interface Write/Read Operations

For write transactions, the station management entity writes data to the addressed SEPHY thus eliminating the requirement for MDIO turnaround. The turnaround time is filled by the management entity by inserting <10>. Figure 7-1 shows the relationship between MDC and the MDIO as driven or received by the station (STA) and SEPHY (PHY) for a typical register write/read access.

The IDLE condition on MDIO is a high-impedance state. All three state drivers are disabled and the SEPHY's pull-up resistor will pull the MDIO line to a logic one.

Figure 7-1 MI Interface Write/Read Operations

| Command | Preamble<br>[31:0] | ST<br>[1:0] | OP<br>[1:0] | PHYADD<br>[4:0] | REAGADD<br>[4:0] | TA<br>[1:0] | DATA<br>[15:0] | IDLE<br>[0] |

|---------|--------------------|-------------|-------------|-----------------|------------------|-------------|----------------|-------------|

| Read    | 111                | 01          | 10          | aaaaa           | RRRRR            | Z0          | DDD            | Z           |

| Write   | 111                | 01          | 01          | aaaaa           | RRRRR            | 10          | DDD            | Z           |

| Table 7-1 - | MI | Interface | Protocol |

|-------------|----|-----------|----------|

|-------------|----|-----------|----------|

# 8 ARCHITECTURE

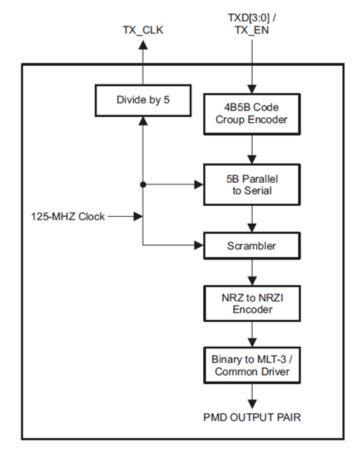

#### 8.1 100BASE-TX Transmitter

The 100BASE-TX transmitter consists of several functional blocks which convert synchronous 4-bit nibble data, as provided by the MII/RMII, to a scrambled MLT-3 125 Mb/s serial data stream. Because the 100BASE-TX TP-PMD is integrated, the differential output pins, PMD output pair, can be directly routed to the magnetics.

The block diagram in provides an overview of each functional block within the 100BASE-TX transmit section.

The transmitter section consists of the following functional blocks:

- Code-group encoder and injection block

- Scrambler block (bypass option)

- NRZ to NRZI encoder block

- Binary to MLT-3 converter

- Output driver

SEPHY implements the 100BASE-TX transmit state machine diagram as specified in the IEEE 802.3u Standard, Clause 24.

Figure 8-1 100BASE-TX Block Diagram

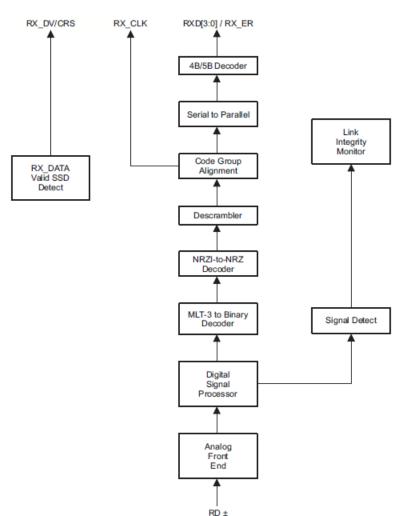

### 8.2 100BASE-TX Receiver

The 100BASE-TX receiver consists of several functional blocks which convert the scrambled MLT-3 125Mb/s serial data stream to synchronous 4-bit nibble data that is provided to the MII/RMII. Because the 100BASE-TX TP-PMD is integrated, the differential input pins, RD±, can be directly routed from the AC coupling magnetics.

See Figure 8-2 for a block diagram of the 100BASE-TX receive function. This provides an overview of each functional block within the 100BASE-TX receive section.

The receive section consists of the following functional blocks:

- Analog front end

- Digital signal processor

- Signal detect

- MLT-3 to binary decoder

- NRZI to NRZ decoder

- Serial to parallel

- Descrambler

- Code group alignment

- 4B/5B decoder

- Link integrity monitor

- Data Valid detection

#### 8.2.1 Analog Front End

In addition to the digital equalization and gain control, SEPHY includes gain and BLW correction in the analog front end.

#### 8.2.2 Digital Signal Processor

The digital signal processor includes adaptive equalization with gain control, clock recovery and base line wander correction.

Figure 8-2 100BASE-TX Receive Block Diagram

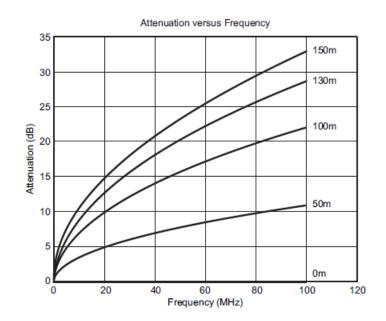

### 8.2.3 Digital Adaptive Equalization and Gain Control

When transmitting data at high speeds over copper twisted pair cable, frequency dependent attenuation becomes a concern. In high-speed twisted pair signalling, the frequency content of the transmitted signal can vary greatly during normal operation based primarily on the randomness of the scrambled data stream. This variation in signal attenuation caused by frequency variations must be compensated to ensure the integrity of the transmission.

In order to ensure quality transmission when employing MLT-3 encoding, the compensation must be able to adapt to various cable lengths and cable types depending on the installed environment. The selection of long cable lengths for a given implementation requires significant compensation which will overcompensate for shorter, less attenuating lengths. Conversely, the selection of short or intermediate cable lengths requiring less compensation will cause serious under-compensation for longer length cables. The compensation or equalization must be adaptive to ensure proper conditioning of the received signal independent of the cable length.

SEPHY utilizes an extremely robust equalization scheme referred as 'digital adaptive equalization'.

The digital equalizer removes inter symbol interference (ISI) from the receive data stream by continuously adapting to provide a filter with the inverse frequency response of the channel. Equalization is combined with an adaptive gain control stage. This enables the receive 'eye pattern' to be opened sufficiently to allow very reliable data recovery.

The curves given in Figure 8-3 illustrate attenuation at certain frequencies for given cable lengths. This is derived from the worst case frequency vs. attenuation figures as specified in the EIA/TIA Bulletin TSB-36.

These curves indicate the significant variations in signal attenuation that must be compensated for by the receive adaptive equalization circuit.

Figure 8-3 EIA/TIA Attenuation vs. Frequency for 0, 50, 100, 130 and 150 meters of CAT 5 cable

SEPHY is completely ANSI TP-PMD compliant and includes base line wander (BLW) compensation. The BLW compensation block can successfully recover the TPPMD defined "killer" pattern. BLW can generally be defined as the change in the average DC content, relatively short period over time, of an AC coupled digital transmission over a given transmission medium. (i.e., copper wire). BLW results from the interaction between the low frequency components of a transmitted bit stream and the frequency response of the AC coupling components within the transmission system. If the low frequency content of the digital bit stream goes below the low frequency pole of the AC coupling transformers then the highpass filter characteristics of the transformers will dominate resulting in potentially serious BLW.

This event can be as large as 800 mV of DC offset for a period of 120  $\mu$ s. If left uncompensated, events such as this can cause packet loss.

### 8.3 10BASE-T Transceiver

The 10BASE-T transceiver module is IEEE 802.3 compliant. It includes the receiver, transmitter, heartbeat, loopback, jabber, and link integrity functions, as defined in the standard. It includes a digital FIR filter in order to shape the output signal to meet the TX template specified in the standard. An external filter is not required on the 10BASE-T interface since this is integrated inside the SEPHY. This section focuses on the general 10BASET system level operation.

#### 8.3.1 Normal Link Pulse Detection/Generation

The link pulse generator produces pulses as defined in the IEEE 802.3 10BASE-T standard. Each link pulse is nominally 100 ns in duration and transmitted every 16 ms in the absence of

transmit data. Link pulses are used to check the integrity of the connection with the remote end. If valid link pulses are not received, the link detector disables the 10BASE-T twisted pair transmitter, receiver and collision detection functions.

#### 8.3.2 Transmit and Receive Filtering

External 10BASE-T filters are not required when using SEPHY, as the required signal conditioning is integrated into the device. Only isolation transformers and impedance matching resistors are required for the 10BASE-T transmit and receive interface. The internal transmit filtering ensures that all the harmonics in the transmit signal are attenuated by at least 30 dB.

#### 8.3.3 Transmitter

The encoder begins operation when the transmit enable input (TX\_EN) goes high and converts NRZ data to preemphasized Manchester data for the transceiver. For the duration of TX\_EN, the serialized transmit data (TXD) is encoded for the transmit-driver pair (PMD Output Pair). TXD must be valid on the rising edge of transmit clock (TX\_CLK). Transmission ends when TX\_EN deasserts. The last transition is always positive; it occurs at the center of the bit cell if the last bit is a one, or at the end of the bit cell if the last bit is a zero.

#### 8.3.4 Receiver

The decoder detects the end of a frame when no additional mid-bit transitions are detected. Within one and a half bit times after the last bit, carrier sense is de-asserted.

# 9 CONFIGURATION

### 9.1 SPEED Pin Control

The SEPHY speed mode can be controlled using the external pin named AN\_SPEED. If set to LOW during power up or reset will set 10BASE-T mode. If set to HIGH will set 100BASE-TX mode. The pin value at power up or reset will be stored at the Control Register (CTRL) at bit SPEEDSEL. This can be also modified via MI interface.

### 9.2 PHY Address

The five PHY address inputs are mapped to the pins 50, 51, 52, 54 and 56. PHYADD[1:0] are shared with TEST\_I[1:0] signals. The PHYADD values are set through the values in those pin at power up or reset.

### 9.3 LED Interface

SEPHY supports three light emitting diode (LED) pins, signalling LINK stablished, RX activity and TX activity.

### 9.4 Internal Loopback

SEPHY includes loopback test mode for facilitating systems diagnosis. The loopback mode is selected through bit 0.14 (LOOPBACK) of the CTRL register. Writing 1 to this bit enables MII transmit data from TX± pins to be routed to the RX± pins. While in Loopback mode the data will not be received from the channel while transmission is kept.

### 9.5 Power Down

SEPHY supports power down mode which is activated forcing LOW at PWRDN\_N pin (39). This mode switches down most of the internal circuitry and reduces power consumption to a minimum.

### 9.6 Clock Input

SEPHY uses an external clock at 25MHz, which should be provided through the CLK\_IN pin (24).

### 9.7 MII/RMII interface

SEPHY includes two different MAC interfaces which can be used MII and RMII. In order to select between them, the RMII\_SEL\_EN pin (9) can be set to HIGH at power up or reset. This can be also performed through bit 19.14 (RMIIEN) of the CTRL1 register.

### 9.8 Power Up Sequence

SEPHY includes analog an digital circuitry with separate power supplies. The power-up sequence required for proper device setup is as follows:

- 1) DVDD and VDD\_PLL will be turned on.

- 2) IOVDD and AVDD will turn on.

- 3) RESET\_N is deasserted at least 20us after the power supplies are stable.

### 9.9 PLL power supply decoupling

The PLL is embedded in a noisy digital circuit and have its output signal jitter increased due to the activity of the circuit. Although the Digital Core ground and the PLL grounds are not internally connected by metal, ground crosstalk mechanisms exist through the common chip substrate.

The PLL has its own power supply pins, vccpll and vsspll. They are connected to specific power supply buffers which are separated from the others by insulation buffers. To better reduce the noise coupling, the power supplies must be decoupled externally with large capacitors, 1uF capacitor and 100nF-10nF ceramic capacitor.

### 9.10 PCB design recommendations

Independent decoupling capacitors shall be placed for each one of the four different power domains: IOVDD, DVDD, VDD\_PLL and AVDD. At least a large 1uF electrolytical capacitor and and 100nF high frequency ceramic capacitor shall be place on each of them, as close to the power pins as possible.

The 100 $\Omega$  termination resistor shall be placed to the MDI\_RX\_P/ MDI\_RX\_M pins as close as possible.

In order to avoid possible bias current mismatches, the PCB track from RBIAS pin to the  $39.2k\Omega$  external resistor shall be as short as possible, including the track from that resistor to ground.

Different ground domains should be tied externally together as close to the chip as possible.

### 9.11 RESET OPERATION

SEPHY operation needs hardware reset after power on to ensure proper functionality. The reset it is synchronized with the LOCK signal provided by the PLL to ensure that reset is deasserted only if a stable clock from the PLL is provided.

If required during normal operation, the device can be reset by a hardware or software reset.

#### 9.11.1 Hardware Reset

A hardware reset is accomplished by applying a low pulse (LVTTL level), with a duration of at least 1  $\mu$ s, to the RESET pin (28). This will reset the device such that all registers will be reinitialized to default values and the hardware configuration values will be re-latched into the device (similar to the power-up/reset operation).

#### 9.11.2 Software Reset

A software reset is accomplished by setting the reset bit (bit 0.15) of the Control register (CTRL). The software reset will reset the device such that all registers will be reset to default values and the hardware configuration values will be maintained. Software driver code must wait TBD following a software reset before allowing further serial MII/RMII operations with SEPHY.

### **10 MI management Registers**

The MI basic register set consists of two registers referred to as the Control register (Register 0) and the Status register (Register 1). All PHYs that provide an MII shall incorporate the basic register set.

Those PHYs that provide a GMII shall incorporate an extended basic register set consisting of the Control register (Register 0), Status register (Register 1), and Extended Status register (Register 15). Registers 2 through 14 are part of the extended register set. SEPHY device do not to provide GMII, but the registers are showing here for convenience.

Register addresses 16 through 31 may be used to provide vendor-specific functions or abilities. In SEPHY, register address 31 provides access to test management interface registers

The device includes a MI interface in order to provide access to MII registers. The MI interface is described in 7.4.

# MII registers definition

| Register | Register         | Used/Not |         | Register                                                      | Basic/Exte | nded |                                                                                                                                                             |

|----------|------------------|----------|---------|---------------------------------------------------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address  | address<br>(HEX) | Used     | TAG     | name                                                          | MII        | GMII |                                                                                                                                                             |

| 0        | 0x00             | Used     | CTRL    | Control                                                       | В          | В    | The <b>MII</b> basic register set consists of two registers referred to as the                                                                              |

| 1        | 0x01             | Used     | STS     | Status                                                        | В          | В    | Control register (Register 0) and the<br>Status register (Register 1). All PHYs<br>that provide an MII shall incorporate<br>the basic register set.         |

| 2,3      | 0x02-0x03        | Not Used | PHYID   | PHY Identifier                                                | E          | E    |                                                                                                                                                             |

| 4        | 0x04             | Not Used | ANA     | Auto-<br>Negotiation<br>Advertisement                         | E          | E    | All PHYs that provide a <b>GMII</b> shall<br>incorporate an extended basic<br>register set consisting of the <b>Control</b>                                 |

| 5        | 0x05             | Not Used | ANLPBPA | Auto-<br>Negotiation<br>Link Partner<br>Base Page<br>Ability  | E          | E    | register (Register 0), Status register<br>(Register 1), and Extended Status<br>register (Register 15). The status and<br>control functions defined here are |

| 6        | 0x06             | Not Used | ANEXP   | Auto-<br>Negotiation<br>Expansion                             | E          | E    | considered basic and fundamental<br>to 100 Mb/s and 1000 Mb/s PHYs.<br>Registers 2 through 14 are part of                                                   |

| 7        | 0x07             | Not Used | ANNPT   | Auto-<br>Negotiation<br>Next Page<br>Transmit                 | E          | E    | the extended register set. The<br>format of Registers 4 through 10 is<br>defined for the specific Auto-<br>Negotiation protocol used (Clause                |

| 8        | 0x08             | Not Used | ANLPRNP | Auto-<br>Negotiation<br>Link Partner<br>Received<br>Next Page | E          | E    | 28 or Clause 37). The format of these<br>registers is selected by the bit<br>settings of Registers 1 and 15.                                                |

| 9                | 0x09      | Not Used | MSCTRL   | MASTER-SLAVE<br>Control<br>Register    | E        | E |                                         |

|------------------|-----------|----------|----------|----------------------------------------|----------|---|-----------------------------------------|

| 10               | 0x0A      | Not Used | MSSTS    | MASTER-SLAVE<br>Status Register        | E        | E |                                         |

| 11               | OxOB      | Not Used | PSECTRL  | PSE Control<br>register                | E        | E |                                         |

| 12               | 0x0C      | Not Used | PSESTS   | PSE Status<br>register                 | E        | E |                                         |

| 13               | 0x0D      | Not Used | MMDCTRL  | MMD Access<br>Control<br>Register      | E        | E |                                         |

| 14               | 0x0E      | Not Used | MMDADD   | MMD Access<br>Address Data<br>Register | E        | E |                                         |

| 15               | OxOF      | Not Used | EXSTS    | Extended<br>Status                     | Reserved | В |                                         |

| 16               | 0x10      | Used     | TXCFG    | TX config                              | E        | Е |                                         |

| 17               | 0x11      | Used     | RXCFG    | RX config                              | E        | Е |                                         |

| 18               | 0x12      | Used     | TESTCFG  | Test config                            | E        | Е | Register addresses 16 through 31        |

| 19               | 0x13      | Used     | CTRL1    | Control 1                              | E        | Е | (decimal) may be used to provide        |

| 20               | 0x14      | Used     | STATUS1  | Status 1                               | E        | Е | vendor-specific functions or abilities. |

| 21 through<br>30 | 0x15-0x1E | Not Used | N/A      | Vendor<br>Specific                     | E        | Е |                                         |

| 31               | RESERVED  | RESERVED | RESERVED | RESERVED                               | -        | - |                                         |

B=BASIC E=EXTENDED

**Sephy**

# Register Bit Acronyms

| ess              | (HEX)                  |               | e              |             |               |              |             |             |               |               | В             | IT            |               |               |               |           |           |           |           |

|------------------|------------------------|---------------|----------------|-------------|---------------|--------------|-------------|-------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----------|-----------|-----------|-----------|

| Register address | Register address (HEX) | TAG           | Register name  | 15          | 14            | 13           | 12          | 11          | 10            | 9             | 8             | 7             | 6             | 5             | 4             | 3         | 2         | 1         | 0         |

| 0                | 0×00                   | CTRL          | Control        | RESET       | LOOPBACK      | SPEEDSELL    | AUTONEGEN   | POWERDWN    | ISOLATE       | RAUTONEGGEN   | DM            | CT            | SPEEDSELM     | UNIDIREN      | N/A           | N/A       | N/A       | N/A       | N/A       |

| 1                | 0x01                   | STS           | Status         | 100BASET4EN | 100BASETXFDEN | 100BASEXHFEN | 10BASETFDEN | 10BASETHDEN | 100BASET2FDEN | 100BASET2HDEN | EXTSTAT       | UNIABI        | MFPREAMSUP    | AUTONEGCOM    | REMFAULT      | AUTONEGAB | LINKSTAT  | JABDET    | EXTCAP    |

| 2                | 0x02                   | PHYIDO        | PHY Identifier | PHYID<18>   | PHYID<17>     | PHYID<16>    | PHYID<15>   | PHYID<14>   | PHYID<13>     | PHYID<12>     | PHYID<11>     | PHYID<10>     | PHYID<9>      | PHYID<8>      | PHYID<7>      | PHYID<6>  | PHYID<5>  | PHYID<4>  | PHYID<3>  |

| 3                | 0x03                   | <b>LUIVHA</b> | PHY Identifier | PHYID<24>   | PHYID<23>     | PHYID<22>    | PHYID<21>   | PHYID<20>   | PHYID<19>     | MODNUM<br><5> | MODNUM<br><4> | MODNUM<br><3> | MODNUM<br><2> | MODNUM<br><1> | MODNUM<br><0> | REVNUM<3> | REVNUM<2> | REVNUM<1> | REVNUM<0> |

| 1<br>6           | 0x10                   | TXCFG         | TX config      | PREAMGENEN  | JABDIS        | TXDIS        | N/A         | N/A         | N/A           | N/A           | N/A           | N/A           | N/A           | N/A           | N/A           | N/A       | N/A       | N/A       | N/A       |

#### D6.13 SEPHY Datasheet SEPHY

| 1<br>7 | 0x11     | RXCFG    | RX config   | RXDIS    | FRCLNK10 | N/A      | N/A      | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

|--------|----------|----------|-------------|----------|----------|----------|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1<br>8 | 0x12     | TESTCFG  | Test config | TESTO<1> | TESTO<0> | TESTI<1> | TESTI<0> | N/A |

| 1<br>9 | 0x13     | CTRL1    | Control 1   | MDIXEN   | RMIIEN   | EEEEN    | N/A      | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

| 2<br>0 | 0x14     | STATUS1  | Status 1    | DESCRLCK | LEDTI    | LEDRI    | N/A      | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

| 3<br>1 | RESERVED | RESERVED | RESERVED    | N/A      | N/A      | N/A      | N/A      | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

### **MII Registers Definition**

### Control Register (0x00)

| Bit(s) | Name                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                 | R/W*      | Default  | Used | Tag             |

|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------|-----------------|

| 0.15   | Reset                                         | <ul> <li>1 = PHY reset</li> <li>0 = normal operation</li> <li>All PHY functions are disabled. At recovery from Reset the PHY does the following:</li> <li>- Initalizes Analog Circuitry</li> <li>- Initializes all digital logic and state machines</li> <li>- Read and latches PHYAD pins</li> <li>- Initilializes MII registers to their default values</li> </ul>                                        | R/W<br>SC | 0        | Y    | RESET           |

| 0.14   | Loopback                                      | 1 = enable loopback mode<br>0 = disable loopback mode                                                                                                                                                                                                                                                                                                                                                       | R/W       | 0        | Y    | LOOPBACK        |

| 0.13   | Speed<br>Selection<br>(LSB) <sup>(1)</sup>    | 1 = 100 Mb/s<br>0 = 10 Mb/s                                                                                                                                                                                                                                                                                                                                                                                 | R/W       | AN_speed | Y    | SPEEDSELL       |

| 0.12   | Auto-<br>Negotiation<br>Enable                | 1 = enable Auto-Negotiation process<br>0 = disable Auto-Negotiation<br>process                                                                                                                                                                                                                                                                                                                              | RO        | 0        | Ν    | AUTONEGEN       |

| 0.11   | Power Down                                    | <ul> <li>1 = power down</li> <li>0 = normal operation**</li> <li>Powers Down all functions but the serial management interface and clock circuitry. Mll registers can be read/written.</li> <li>- Initializes all digital logic and state machines</li> <li>- Mll registers are not reset to default</li> <li>- PHYAD pins are not re-read</li> </ul>                                                       | R/W       | 0        | Y    | POWERDWN        |

| 0.10   | Isolate                                       | 1 = electrically Isolate PHY from MII or OMIT<br>0 = normal operation**                                                                                                                                                                                                                                                                                                                                     | R/W       | 0        | Y    | ISOLATE         |

| 0.9    | Restart<br>Auto-<br>Negotiation               | 1 = restart Auto-Negotiation process<br>0 = normal operation                                                                                                                                                                                                                                                                                                                                                | RO        | 0        | Ν    | RAUTONEGGE<br>N |

| 0.8    | Duplex<br>Mode                                | 1 = full duplex<br>0 = half duplex                                                                                                                                                                                                                                                                                                                                                                          | RO        | 1        | Ν    | DM              |

| 0.7    | Collision Test                                | 1 = enable COL signal test<br>0 = disable COL signal test                                                                                                                                                                                                                                                                                                                                                   | RO        | 0        | Ν    | CT              |

| 0.6    | Speed<br>Selection<br>(MSB)                   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                    | RO        | 0        | Ν    | SPEEDSELM       |

| 0.5    | Unidirectional<br>enable                      | When bit 0.12 is one or bit 0.8 is zero, this<br>bit is ignored. When bit 0.12 is zero and bit<br>0.8 is one:<br>1 = Enable transmit from media<br>independent interface regardless of<br>whether the PHY has determined that a<br>valid link has been established<br>0 = Enable transmit from media<br>independent interface only when the PHY<br>has determined that a valid link has been<br>established | R/W       | 0        | Y    | UNIDIREN        |

| 0.4:0  | Reserved for<br>future<br>standardizat<br>ion | Write as 0, ignore on read                                                                                                                                                                                                                                                                                                                                                                                  | RO        | 0        | Ν    | N/A             |

\*R0 = Read only, LL = Latching low, LH = Latching high, SC=Self Clear (1) The default value it is set by the value of AN\_SPEED pin after reset.

# Status Register (0x01)

| Bit(s) | Name                             | Description                                                                                                                                                                                                                                                                                         | R/W*      | Default | Used | Tag           |

|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------|---------------|

| 1.15   | 100BASE-T4                       | 1 = PHY able to perform 100BASE-T4<br>0 = PHY not able to perform 100BASE-T4                                                                                                                                                                                                                        | RO        | 0       | Y    | 100BASET4EN   |

| 1.14   | 100BASE-TX Full<br>Duplex        | 1 = PHY able to perform full duplex<br>100BASE-TX<br>0 = PHY not able to perform full duplex<br>100BASE-TX                                                                                                                                                                                          | RO        | 1       | Y    | 100BASETXFDEN |

| 1.13   | 100BASE-X Half<br>Duplex         | 1 = PHY able to perform half duplex<br>100BASE-X<br>0 = PHY not able to perform half duplex<br>100BASE-X                                                                                                                                                                                            | RO        | 0       | Y    | 100BASEXHFEN  |

| 1.12   | 10BASE-T Full<br>Duplex          | 1 = PHY able to operate at 10BASE-T in<br>full duplex mode<br>0 = PHY not able to operate at 10BASE-T<br>in full duplex mode                                                                                                                                                                        | RO        | 1       | Y    | 10BASETFDEN   |

| 1.11   | 10BASE-T Half<br>Duplex          | 1 = PHY able to operate at 10BASE-T in<br>half duplex mode<br>0 = PHY not able to operate at 10BASE-T<br>in half duplex mode                                                                                                                                                                        | RO        | 0       | Y    | 10BASETHDEN   |

| 1.10   | 100BASE-T2 Full<br>Duplex        | 1= PHY able to perform full duplex<br>100BASE-T2<br>0 = PHY not able to perform full duplex<br>100BASE-T2                                                                                                                                                                                           | RO        | 0       | Y    | 100BASET2FDEN |

| 1.9    | 100BASE-T2 Half<br>Duplex        | 1 = PHY able to perform half duplex<br>100BASE-T2<br>0 = PHY not able to perform half duplex<br>100BASE-T2                                                                                                                                                                                          | RO        | 0       | Y    | 100BASET2HDEN |

| 1.8    | Extended<br>Status               | 1 = Extended status information in<br>Register 15<br>0 = No extended status information in<br>Register 15                                                                                                                                                                                           | RO        | 0       | Y    | EXTSTAT       |

| 1.7    | Unidirectional<br>ability        | 1= PHY able to transmit from media<br>independent interface regardless of<br>whether the PHY has determined that a<br>valid link has been established<br>0 = PHY able to transmit from media<br>independent interface only when the<br>PHY has determined that a valid link has<br>been established | RO        | 1       | Y    | UNIABI        |

| 1.6    | MF Preamble<br>Suppression       | <ul> <li>1 = PHY will accept management</li> <li>frames with preamble suppressed.</li> <li>0 = PHY will not accept management</li> <li>frames with preamble suppressed.</li> </ul>                                                                                                                  | RO        | 1       | Y    | MFPREAMSUP    |

| 1.5    | Auto-<br>Negotiation<br>Complete | 1 = Auto-Negotiation process<br>completed<br>0 = Auto-Negotiation process not<br>completed                                                                                                                                                                                                          | RO        | 0       | Y    | AUTONEGCOM    |

| 1.4    | Remote Fault                     | 1 = remote fault condition detected<br>0 = no remote fault condition detected                                                                                                                                                                                                                       | RO/<br>LH | 0       | Y    | REMFAULT      |

| 1.3    | Auto-<br>Negotiation<br>Ability  | 1 = PHY is able to perform Auto-<br>Negotiation<br>0 = PHY is not able to perform Auto-<br>Negotiation                                                                                                                                                                                              | RO        | 0       | Y    | AUTONEGAB     |

| 1.2    | Link Status                      | 1 = link is up<br>0 = link is down                                                                                                                                                                                                                                                                  | RO/<br>LL | 0       | Y    | LINKSTAT      |

| 1.1    | Jabber Detect                    | 1 = jabber condition detected<br>0 = no jabber condition detected                                                                                                                                                                                                                                   | RO/<br>LH | 0       | Y    | JABDET        |

| 1.0    | Extended<br>Capability           | 1 = extended register capabilities<br>0 = basic register set capabilities only                                                                                                                                                                                                                      | RO        | 0       | Y    | EXTCAP        |

\*R0 = Read only, LL = Latching low, LH = Latching high, SC=Self Clear

## PHY Identifier Register 1 (0x02)

| Bit(s) | Name                      | Description                                         | R/W* | Default | Used | Tag       |

|--------|---------------------------|-----------------------------------------------------|------|---------|------|-----------|

| 2.15   |                           |                                                     |      |         |      | PHYID<18> |

| 2.14   |                           |                                                     |      |         |      | PHYID<17> |

| 2.13   |                           |                                                     |      |         |      | PHYID<16> |

| 2.12   |                           |                                                     |      |         |      | PHYID<15> |

| 2.11   |                           |                                                     |      |         |      | PHYID<14> |

| 2.10   |                           |                                                     |      |         |      | PHYID<13> |

| 2.9    | DUIV                      | Organizationally Unique Identifier (OUI), Bits 18:3 |      |         |      | PHYID<12> |

| 2.8    | PHY                       |                                                     |      |         | v    | PHYID<11> |

| 2.7    | Identifier<br>Bits (18:3) |                                                     | RO   | TBD Y   | ř    | PHYID<10> |

| 2.6    | DIIS (10.3)               |                                                     |      |         |      | PHYID<9>  |

| 2.5    |                           |                                                     |      |         |      | PHYID<8>  |

| 2.4    |                           |                                                     |      |         |      | PHYID<7>  |

| 2.3    |                           |                                                     |      |         |      | PHYID<6>  |

| 2.2    |                           |                                                     |      |         |      | PHYID<5>  |

| 2.1    |                           |                                                     |      |         |      | PHYID<4>  |

| 2.0    |                           |                                                     |      |         |      | PHYID<3>  |

\*R0 = Read only, LL = Latching low, LH = Latching high

## PHY Identifier Register 1 (0x03)

| Bit(s) | Name                        | Description                  | R/W* | Default | Used | Tag       |

|--------|-----------------------------|------------------------------|------|---------|------|-----------|

| 3.15   |                             |                              |      |         |      | PHYID<24> |

| 3.14   |                             |                              |      |         |      | PHYID<23> |

| 3.13   | PUV Identifier Bits (24:10) | Organizationally Unique      | RO   | TBD     | Y    | PHYID<22> |

| 3.12   | PHY Identifier Bits (24:19) | Identifier (OUI), Bits 24:19 | ĸO   | IBD     | T    | PHYID<21> |

| 3.11   |                             |                              |      |         |      | PHYID<20> |

| 3.10   |                             |                              |      |         |      | PHYID<19> |

| 3.9    |                             |                              |      |         |      | MODNUM<5> |

| 3.8    |                             | Model Number                 | RO   | TBD     |      | MODNUM<4> |

| 3.7    | Model Number                |                              |      |         | v    | MODNUM<3> |

| 3.6    | Model Northbel              | Model Nombel                 | ĸŎ   |         | I    | MODNUM<2> |

| 3.5    |                             |                              |      |         |      | MODNUM<1> |

| 3.4    |                             |                              |      |         |      | MODNUM<0> |

| 3.3    |                             |                              |      |         |      | REVNUM<3> |

| 3.2    | Revision Number             | Revision Number              | RO   | 0       | Y    | REVNUM<2> |

| 3.1    | Kevision nomber             | Kevision normbel             | ĸŬ   |         | 1    | REVNUM<1> |

| 3.0    |                             |                              |      |         |      | REVNUM<0> |

\*R0 = Read only, LL = Latching low, LH = Latching high

## TX config (0x10)

| Bit(s) | Name                             | Description                                                                                                                             | R/W* | Default | Used | Tag        |

|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------------|

| 16.15  | Preamble<br>Generation<br>Enable | <ul> <li>1 = Enable preamble generation for</li> <li>10BASE-T</li> <li>0 = Disable preamble generation</li> <li>for 10BASE-T</li> </ul> | RO   | 0       | Y    | PREAMGENEN |

| 16.14  | Jabber Disable<br>(10BASE-T)     | 1 = Disable Jabber for 10BASE-T<br>0 = Enable Jabber for 10BASE-T                                                                       | R/W  | 0       | Y    | JABDIS     |

| 16.13  | TX_disable                       | 1 = Disable Transmitter<br>0 = Enable Transmitter                                                                                       | R/W  | 0       | Y    | TXDIS      |

| 16.12  | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.11  | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.10  | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.9   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.8   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.7   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.6   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.5   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.4   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.3   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.2   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.1   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

| 16.0   | N/A                              | For Future Use                                                                                                                          | R/W  | 0       | Ν    | N/A        |

\*R0 = Read only, LL = Latching low, LH = Latching high

## RX config (0x11)

| Bit(s) | Name                   | Description                                                                                    | R/W* | Default | Used | Tag      |

|--------|------------------------|------------------------------------------------------------------------------------------------|------|---------|------|----------|

| 17.15  | RX disable             | 1 = Disable Receiver<br>0 = Enable Receiver                                                    | R/W  | 0       | Y    | RXDIS    |

| 17.14  | Force Link<br>10BASE-T | 1 = Force Link OK in RX for<br>10BASE-T mode<br>0 = Normal Link operation<br>for 10BASE-T mode | R/W  | 0       | Y    | FRCLNK10 |

| 17.13  | N/A                    | For Future Use                                                                                 | R/W  | 0       | Y    | N/A      |

| 17.12  | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.11  | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.10  | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.9   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17,8   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.7   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.6   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.5   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.4   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.3   | N/A                    | For Future Use                                                                                 | R/W  | 0       | N    | N/A      |

| 17.2   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.1   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

| 17.0   | N/A                    | For Future Use                                                                                 | R/W  | 0       | Ν    | N/A      |

\*R0 = Read only, LL = Latching low, LH = Latching high

## Test config (0x12)

| Bit(s) | Name        | Description                                                                                          | R/W* | Default | Used | Tag      |

|--------|-------------|------------------------------------------------------------------------------------------------------|------|---------|------|----------|

| 18.15  |             | 1 = Set TEST_O<1> pin to '1'<br>0 = Set TEST_O<1> pin to '0'                                         | R/W  | 0       | Y    | TESTO<1> |

| 18.14  | TEST_O<1:0> | 1 = Set TEST_O<0> pin to '1'<br>0 = Set TEST_O<0> pin to '0'                                         | R/W  | 0       | Y    | TESTO<0> |

| 18.13  |             | 1 = TEST_<1> pin is pulled to '1'<br>externally<br>0 = TEST_<1> pin is pulled to '0'<br>externally   | RO   | 0       | Y    | TESTI<1> |

| 18.12  |             | 1 = TEST_I<0> pin is pulled to '1'<br>externally<br>0 = TEST_I<0> pin is pulled to '0'<br>externally | RO   | 0       | Y    | TESTI<0> |

| 18.11  | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.10  | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.9   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.8   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.7   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.6   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.5   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.4   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.3   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.2   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.1   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

| 18.0   | N/A         | For Future Use                                                                                       | RO   | 0       | Ν    | N/A      |

\*R0 = Read only, LL = Latching low, LH = Latching high

## Control 1 config (0x13)

| Bit(s) | Name                  | Description                                           | R/W* | Default                           | Used | Tag    |

|--------|-----------------------|-------------------------------------------------------|------|-----------------------------------|------|--------|

| 19.15  | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.14  | RMII Interface Enable | 1 = Enable RMII interface<br>0 = Enable MII interface | R/W  | RMII_SEL_en<br>pin <sup>(1)</sup> | Y    | RMIIEN |

| 19.13  | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.12  | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.11  | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.10  | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.9   | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.8   | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.7   | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |

| 19.6   | N/A                   | For Future Use                                        | RO   | 0                                 | Ν    | N/A    |